编辑点评:数字集成电路的设计方法与流程

ASIC设计理论与实践——RTL 验证、综合与版图设计电子书详细介绍了数字集成电路的设计理论与实践方法,通过一个完整的CPU电路RTL级验证、综合及版图设计,让读者系统、全面地了解ASIC设计流程。

ASIC设计理论与实践电子文档图片预览

图书亮点

超深亚微米时代集成电路设计方法与设计工具

通过模块化实例来打通ASIC设计各阶段要领

用模块集成来完成一个完整的CPU设计

源于多年课程实践的积累,培养集成电路设计人才,实现真正“中国芯”

内容简介

本书主要介绍了数字集成电路的设计理论与实践方法,通过一个完整的CPU电路RTL级验证、综合及版图设计,让读者系统、全面地了解ASIC设计流程。本书主要内容包括:ASIC设计方法概述、设计流程及各阶段用到的设计仿真工具;VerilogHDL基础语法及测试程序建模方法概述;ASIC设计实验环境搭建;CPU基本原理、相关指令系统及对应的功能实现;RTL级设计及仿真、电路综合以及版图设计等各层次概念及物理意义等。

本书内容翔实,图文并茂,由浅入深地介绍了数字集成电路的设计方法与流程,以ASIC理论、CPU基本理论为支撑,结合VerilogHDL语法基础,用“实验+验证”的实例方式讲解ASIC设计各阶段流程,使读者能快速上手,并且为以后的ASIC设计打下坚实的基础。本书设计实例基于Synopsys公司的相关EDA工具。

本书可作为高等院校电子科学与技术、电子信息科学与技术、计算机科学与技术、通信工程等专业的本科生或研究生教材,也可作为相关专业教师或设计工程师的学习参考资料。

关于作者

刘雯,任教于北京邮电大学电子工程学院,主要研究方向为室内外高精度定位技术及位置服务。主持国家重点研发计划课题和国家国家自然科学基金面上项目各1项,主持完成国家863课题1项;获得国家科技发明二等奖和国家科技进步二等奖各1项,教育部、中国电子学会、中国通信学会等省部级奖励7项指导学生参加全国研究生电子设计大赛赛获得初赛一等奖;在国际期刊及相关专业国际会议发表学术论文30余篇。

目录大全

第1章ASIC概述1

1.1 ASIC概念 2

1.2 ASIC设计方法 3

1.3 ASIC设计流程 4

1.3.1 设计需求分析 4

1.3.2 模块设计及验证 5

1.3.3 逻辑综合及验证 6

1.3.4 版图设计 6

1.3.5 参数提取与静态时序分析 6

1.3.6 物理验证 7

1.4 集成电路设计工具 7

1.4.1 EDA公司简介 7

1.4.2 设计流程各阶段所用工具 8

1.5 全书架构 10

第 2章VerilogHDL基础及实验环境 11

2.1 VerilogHDL硬件描述语言 11

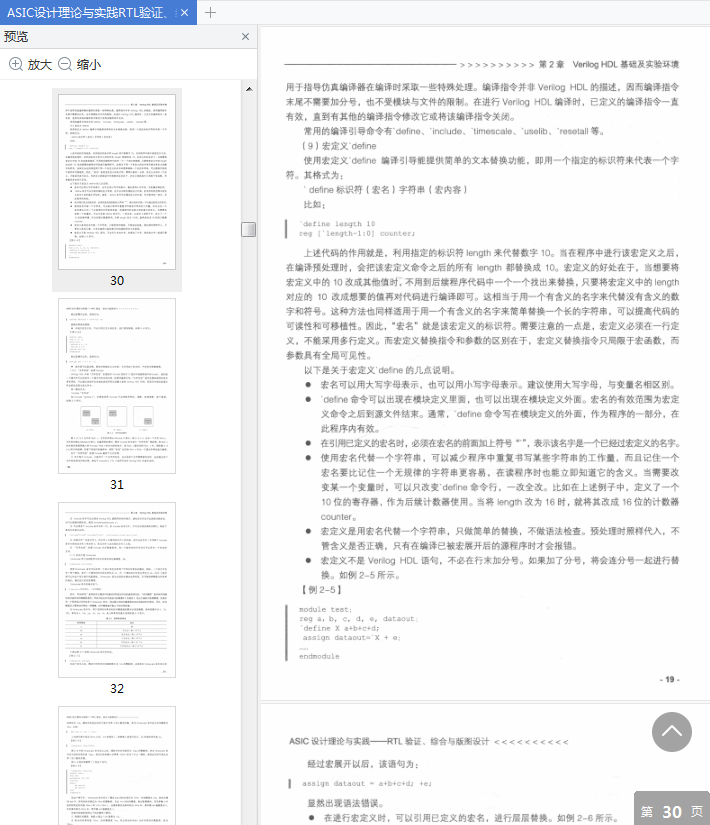

2.1.1 VerilogHDL语法基础 12

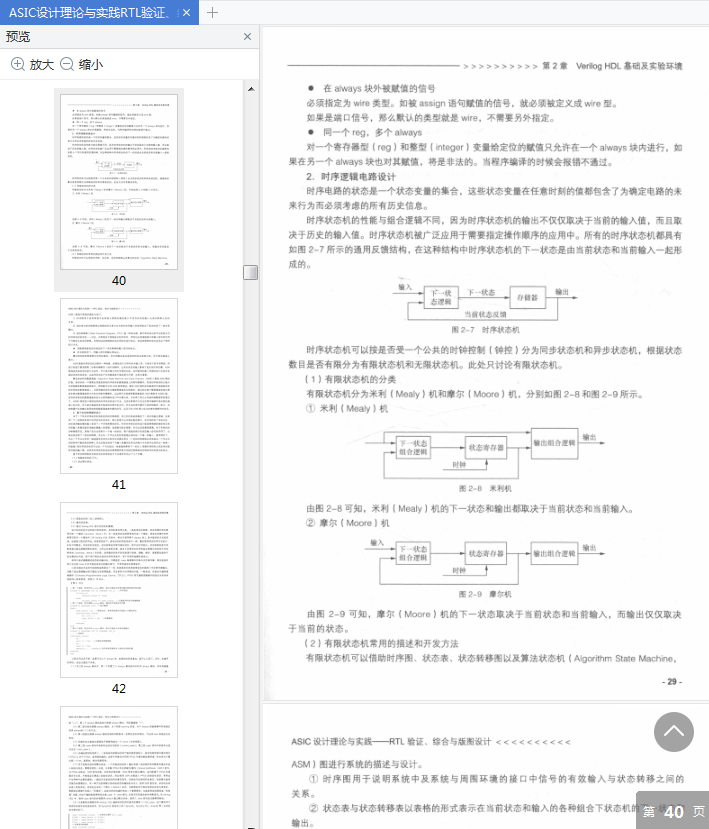

2.1.2 VerilogHDL模块设计 24

2.1.3 VerilogHDL测试程序建模方法 33

2.1.4 VerilogHDL的编写技巧 38

2.2 ASIC设计工具运行环境 40

2.2.1 Linux组成结构 40

2.2.2 环境变量设置 43

2.2.3 Linux相关命令 45

第3章 中央处理器 48

3.1 CPU概述 48

3.2 CPU的指令系统 49

3.2.1 指令的基本格式 49

3.2.2 指令分类 50

3.2.3 寻址方式 52

3.2.4 指令周期 54

3.3 CPU的功能实现 55

3.3.1 存储器 55

3.3.2 程序计数器 55

3.3.3 指令寄存器 56

3.3.4 地址多路选择器 56

3.3.5 算术逻辑单元 57

3.3.6 累加器 57

3.3.7 状态控制器 58

3.3.8 CPU 59

第4章 RISC_CPURTL级设计及仿真 60

4.1 RISC_CPU设计流程 60

4.2 RTL编译与仿真工具使用 60

4.3 RTL级设计与仿真 62

4.3.1 选择器设计 62

4.3.2 程序计数器设计 64

4.3.3 指令寄存器设计 66

4.3.4 算术逻辑单元设计 69

4.3.5 存储器设计 72

4.3.6 设计时序逻辑时采用阻塞赋值与非阻塞赋值的区别 75

4.3.7 状态控制器设计 77

4.3.8 CPU集成设计及验证 81

第5章 电路综合 86

5.1 逻辑综合 86

5.1.1 逻辑综合定义 86

5.1.2 数字同步电路模型 86

5.1.3 时序驱动电路设计 89

5.1.4 综合的三个阶段和综合的层次 90

5.2 基于DesignCompiler的逻辑综合流程 92

5.2.1 逻辑综合流程 92

5.2.2 设置库文件 92

5.2.3 读入设计文件 94

5.2.4 施加设计约束 94

5.2.5 定义环境属性 97

5.2.6 综合及结果输出 98

5.2.7 结果分析 99

5.2.8 综合后仿真 101

5.3 综合实验 102

5.3.1 建立工作目录 102

5.3.2 设置工作环境 103

5.3.3 添加PAD 104

5.3.4 编写综合脚本 105

5.3.5 综合的执行 106

5.3.6 综合结果分析 106

5.3.7 门级电路仿真 109

第6章 版图设计 110

6.1 版图设计定义及内容 110

6.1.1 版图设计定义 110

6.1.2 版图设计的输入输出 110

6.1.3 版图设计用到的库文件 111

6.2 基于ICCompiler的版图设计流程 113

6.2.1 ICC的启动和关闭 114

6.2.2 数据准备 115

6.2.3 布图规划 115

6.2.4 布局 118

6.2.5 时钟树综合 118

6.2.6 布线 119

6.2.7 参数提取和后仿真 120

6.2.8 物理验证 121

6.3 版图设计实验 121

6.3.1 实验内容和目的 121

6.3.2 实验指导 121

附录一 Verilog语言要素 135

附录二 各阶段常用命令使用说明 148

附录三 Linux常用命令及说明 153

参考文献 157

下载体验